DDR5 memory specification update expands maximum data transfer speed to 8800Mbps and adds anti-row hammer function

On April 17, 2024,

JEDEC Updates JESD79-5C DDR5 SDRAM Standard: Elevating Performance and Security for Next-Gen Technologies | JEDEC

https://www.jedec.org/news/pressreleases/jedec-updates-jesd79-5c-ddr5-sdram-standard-elevating-performance-and-security

JEDEC Extends DDR5 Memory Specification to 8800 MT/s, Adds Anti-Rowhammer Features

At the time of writing, JEDEC announced the specifications for DDR5, a widely used DRAM standard, in July 2020, which stated that the maximum data transfer speed of DDR5 at the time of commercialization would reach 6400 Mbps.

JEDEC announces the final specification of the next-generation memory standard 'DDR5', what has evolved from DDR4? - GIGAZINE

However, in recent years, advances in technology have made it possible to manufacture faster memory. On April 17, 2024, JEDEC updated the DDR5 standard, naming the DDR5 standard ' JESD79-5C .'

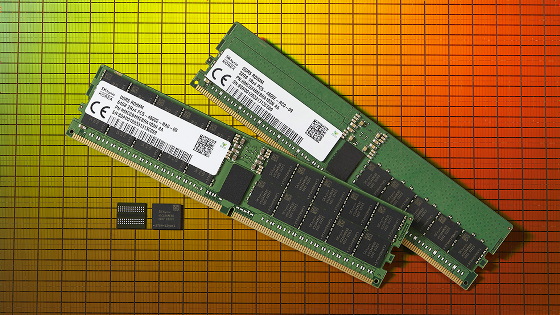

JESD79-5C increases the maximum data transfer rate from 6800Mbps to 8800Mbps by including support for some memory timings that were not previously included.

In addition, a feature called 'Self-Refresh Exit Clock Sync' has been added to optimize I/O training, and Dual-Die Package (DDP) timing has been incorporated.

In addition, an 'anti-row hammer' function has been added that intervenes in the memory controller to protect memory IP from memory-targeting row hammer attacks. One of the anti-row hammer functions, 'Per-Row Activation Counting (PRAC)', can count the frequency with which a memory row is activated, and this information allows the memory controller to identify overly activated memory rows and stabilize the data by performing appropriate updates.

However, the updated DDR5 standard removes support for a mechanism called '

'We are pleased to announce JEDEC's efforts to advance the DDR5 standard,' said Mian Qudus, chairman of the JEDEC board of directors. 'JESD79-5C is intended to support the evolving demands of the technology industry, including increased security, improved reliability and improved performance across a wide range of applications.'

'The addition of PRAC, a comprehensive solution for protecting DRAM data, was an essential part of this update to the DDR5 standard,' said Christopher Fox, chairman of JEDEC's Committee 42. 'Work is underway in Committee 42 to incorporate PRAC into other DRAM products within JEDEC.'

Related Posts: